「SSDやメモリ等をCPUから離れた場所に配置して、必要に応じてアクセスし利用するディスアグリゲーテッドコンピューティングの実現において、PCIe光接続は重要な役割を果たす」

2025年6月、PCI Express(PCIe)の規格策定・管理を行うPCI-SIG※1が、光接続を可能にする新仕様を発表した。「コンピューター内」「電気信号」を前提に進化してきたPCIe通信を光ファイバー上で可能にするこの新規格の可能性について、京セラ 研究開発本部 フォトニクス事業開発部 フォトニックモジュール開発部の赤星知幸氏はそう話す。

※1 PCI-SIG1992年に設立。拡張インターフェース規格であるPCI規格の策定と管理を行う。PCIは当初、インテルの独自仕様だったが、PCI-SIGに引き継がれた。現在はPCI Express(PCIe)規格などの策定を行っている。約1000の企業・団体が所属する

京セラ 研究開発本部 フォトニクス事業開発部 フォトニックモジュール開発部 工学博士 赤星知幸氏

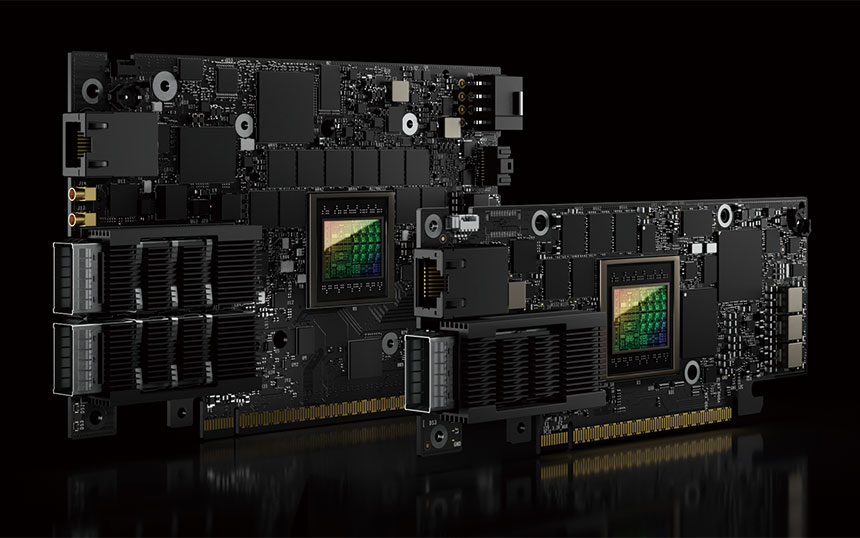

PCIeは、マザーボードと周辺機器を接続するための高速な拡張バス規格として2002年に最初の仕様(PCIe 1.0)が誕生。業界標準のI/Oインターフェースとしてその後も進化を続けてきた。今回、最新世代「PCIe 7.0」のリリースと同時に、PCIeを光通信に対応させる新仕様「Optical Aware Retimer Engineering Change Notice」(OARECN)が発表された。このOAE-ECNは、最新のPCIe 7.0仕様だけでなく、PCIe 6.4にも追加される。

PCIe「光化」の理由とは

光化の目的は、PCIe接続の大容量化、低消費電力化だけではない。イーサネットに比べて低遅延なPCIe接続をサーバー間、ラック間やポッド間の接続に延伸することも目的の1つである。

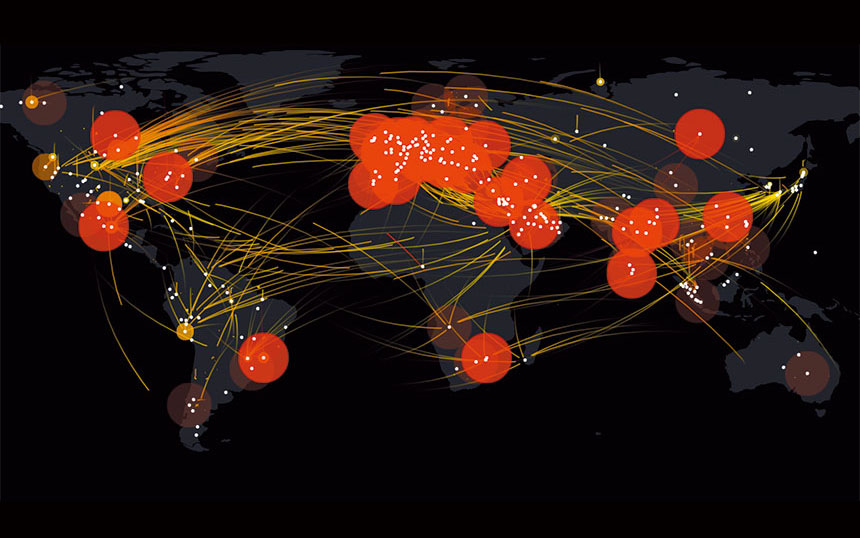

データセンター内の装置間/ラック間の通信には現在、イーサネットやInfiniBandが使われている。そこに「光版PCIe」が加わることで何が起こるのか。

その前に、PCIe規格の特徴についておさらいしておこう。

PCIeは約3年ごとに新世代が登場し、その度に通信帯域が倍増してきた(図表1)。

図表1 PCIe規格の策定年度と伝送速度の推移

複数の伝送路(レーン)を束ねて伝送容量を拡大できるのがPCIeの特徴であり、例えば、通信帯域32GbpsのPCIe 5.0なら、16レーンで512Gbpsの大容量伝送が可能になる。

注意が必要なのは、規格策定から製品化までの期間が長いことだ。

赤星氏によれば、新世代の規格策定から対応サーバーの製品化にはこれまで3年ほどかかっている。2019年に規格化された第5世代(Gen5)のPCIe 5.0に対応したサーバーが2023年にようやく販売開始され、現在、データセンターで導入・活用され始めている。

現時点ではPCIe 7.0(通信帯域128Gbps)はおろか、2022年策定のPCIe 6.0(64Gbps)対応サーバーもまだ市場投入されていない状況だ。現在はPCIe 6.0がPoCの段階で、来年以降に製品化と見られる。